## **JEMIO**

### JTAG External Modules for Cluster Test

The StarTest JEMIO module main features are:

- **ü** Performs both Interconnect and Cluster tests in circuit boards

- **ü** Tests for opens all PWR and GND pins of the GPIO sets

- ii JTAG controlled GPIO nets for drive and sense

- ii Each I/O pin is independently controlled for sense, drive, bi-directional, and tri-state function

- **ü** Keyed flat connector compatibility

- ii Hot Swap: each module may be connected/disconnected between tests without switching power off

- **ü** Equipped with the JTAG/IEEE 1149.1 (JEMIO.1) and IEEE 1149.6 (JEMIO.6) Test Access Port (TAP)

- **ü** Supplied software contains BSDL file of the module

- **ü** Full compatibility with the following JTAG vendor ATPG and Runner platforms:

- Flynn Systems' on TAP Series 4000

- - Corelis' ScanExpress

- JTAG Technologies' ProVision

- Asset' ScanWorks

- Goepel' CASCON

- XJTAG' XJRunner

### **JEMIO**

**ü** Supports the wide range of GPIO net sets, including:

#### Module Name

#### Ordering Part Number

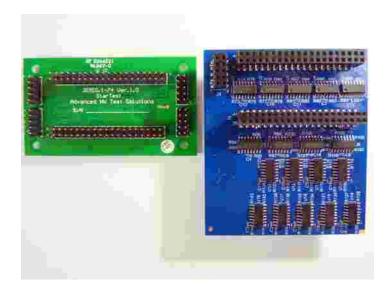

| n | 74 pin JEMIO.1      | JEMIO.1-74      |  |

|---|---------------------|-----------------|--|

| n | 148 pin JEMIO.1     | JEMIO.1-148     |  |

| n | 38 pin JEMIO.1-LVDS | JEMIO.1-LVDS-38 |  |

| n | yyy pin JEMIO.6     | JEMIO.1-yyy     |  |

| n | xx pin JEMIO.1-UD   | JEMIO.1-UDxx    |  |

|   | •                   |                 |  |

Consult StarTest for additional GPIO net sets (UDxx means — Upon Demand with xx IOs.

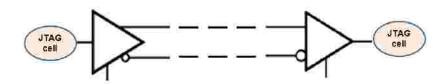

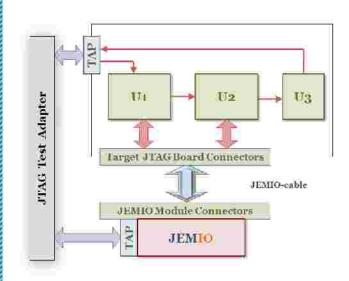

The JEMIO modules family provides a number of sets of JTAG accessible GPIOs or nets that can be used to control and observe signals that go off the board. Each JTAG channel is controlled individually and can be configured as an input, output, or tri-state. The JEMIO scan chain can be combined with the JTAG scan chains of the board being tested so it is included in the infrastructure verification and interconnect tests. Eventually, the JEMIO modules should be used separately or designed into the board or system test fixture. The JEMIO modules provide a flexible and low cost opportunity for JTAG test implementation for the board headers, edge connectors, PCB test points and pads, etc.

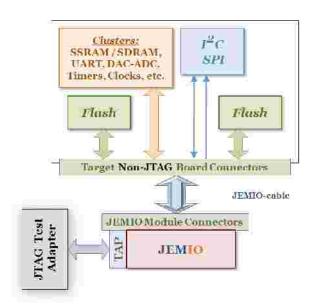

JEMIO test setup for JTAG boards

JEMIO test setup for non-JTAG boards

# **JEMIO**

We would like to present to our hardware valuable customers a new product - the JEMIO-LVDS module. In the full configuration it provides an effective addition to JEMIO the 36 LVDS input and 36 LVDS output channels as well as 2 TTL IO channels. The module can be configured by the customer's demand. Unused LVDS channels remain to be standard JEMIO TTL IO channels.