|

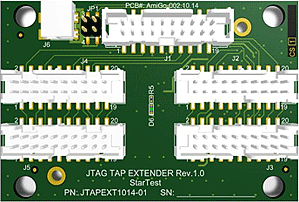

JTAG TAP EXTENDER MODULE (JTAPEXT)

JTAG TAP Extender module designed for using with single or double TAP controllers and allows to extend single primary TAP connection to up to 4 serially connected JTAG chains. JTAG TAP Extender module has the following properties:

JTAG TAP Distributor Tool (TAP-Di)The TAP Distributor TAP-Di is intended for the on-the-fly reconfiguration of the in-circuit JTAG chains during the test sequence execution or before the test starting. The TAP-Di is accessible in the following configurations and all possible sub-configurations:

The TAP Distributor TAP-Di allows any sequence and any number (up to 16) of the secondary TAPs (STAPs) or JTAG chains. The TAP-Di tool automatically recognizes the installed STAPs and allows user automatically build the reconfigured test sequences for secondary JTAG chains with any combination of a STAP voltages (3.3V, 2.5V, 1.8V, 1.5V). For example, if there are four user's secondary JTAG chains: Ib (3V3), Ic (2V5), Id (1V8), and Ie (1V5), the primary TAP might be connected to any of the following JTAG chain combinations and sequences:

The TAP-Di tool provides the gang (concurrent) mode for several identical JTAG chains testing.

The expected signature (CRC or LFSR) of any TDO signal is calculating using the special CRC algorithm and comparing with the Known-Good-Board value.

There is no multi-drop architecture used in the  Fig. 1. TAP-Di Common Diagram

The special TAP-Di gang mode (Gang-F) is intended for the simultaneous burn-in of a number of similar Flash devices connected to a number of the STAP ports. Such burn-in setup significantly increases the Flash programming throughput in the board mass production. For example, if the burn-in time of a Flash device on a board is N sec and you are going to burn-in a batch of K boards, with connection of all K boards to the TAP-Di in the Gang-F mode the total burn-in elapsed time have to be N/K instead of N*K! In addition to single device and gang Flash programming, both for boards with the JTAG support (Fig. 3), and for non-JTAG boards (Fig. 4), the TAP-Di tool has a range of options to test and program an array (eight pairs) of in-circuit serial buses, including SMBus, SPI, I2C, and MicroWire (Fig. 1). The remarkable feature of the TAP-Di tool are four (4) in-circuit DC voltage measurement inputs (Fig. 1). This analog JTAG measurement option is intended for the in-circuit DC voltage verification and monitoring with JTAG tools of any vendor. The TAP-Di tool is also equipped with 32 external JTAG-controllable outputs (Fig. 1) that are intended for any in-circuit JTAG constraints or/and setup support. The TAP-Di tool can be used by test and production engineers to broaden the scope of their in-system device programming facilities without adding much, if any, additional hardware. The TAP-Di tool enables manufacturers of PCBs employing multivendor JTAG test programs for test, in-system programming and Flash burning. The Burn-in Header is the regular 10-pin male header with the standard Altera pin-out. The Master Header is the regular 20-pin male header that in addition to the regular five JTAG pins is equipped with the following 3 additional pins: CONFIG, /WE, RDY/BSY. The CONFIG pin of the Master header is dedicated to switch the TAP-Di internal circuitry between two functional modes:

Each Secondary TAP Header is the regular 20-pin male header that in addition to the regular five JTAG pins is equipped with the following 3 additional pins: PRESENCE, /WE, RDY/BSY. The PRESENCE pin of each STAP header is dedicated to interrogate that the corresponding JTAG chain is actually connected to the STAP header. The TAP-Di tool key benefits are the following:

The TAP Distributor TAP-Di is fully compatible with the following JTAG vendor ATPG and Runner platforms:

|

|

||||||||||||||||||||||||||||||||||

| Site map | About Us | Solutions | Products | StarTest™ Library | Partners and Customers | Support | Monograph | ||

| Contact Webmaster |

© StarTest™. All rights reserved |

|

EXPERIENCED TEST EXPERTS

EXPERIENCED TEST EXPERTS